⌘ Verilog_MIPS_CPU

github.com/Shaan106/ECE_350/Final_CPU

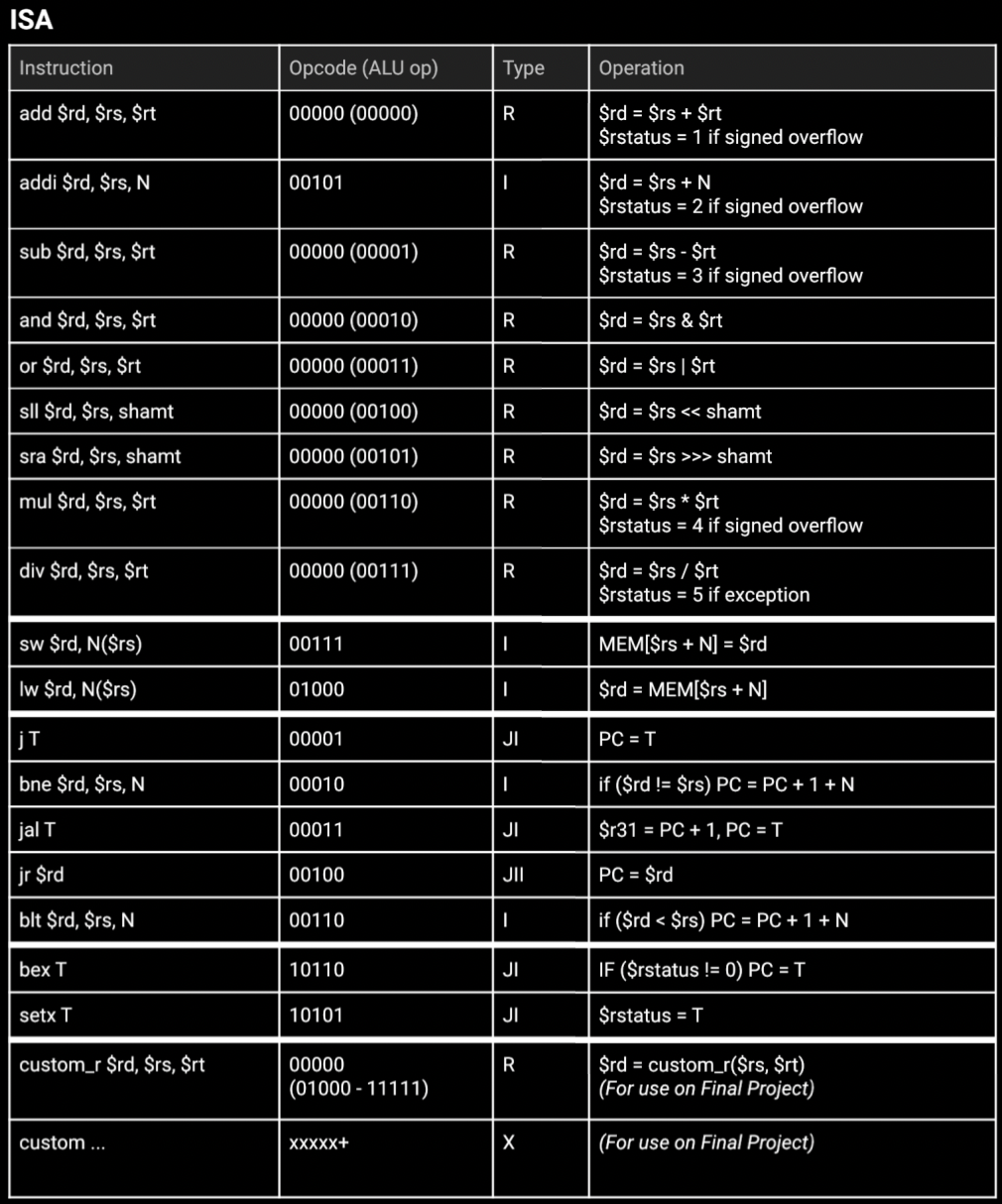

This CPU came out of the Digital Systems course at Duke University. It is a fully functioning 5 stage, pipelined, bypassed, error handling MIPS CPU. Its instruction set can be seen here on the right.

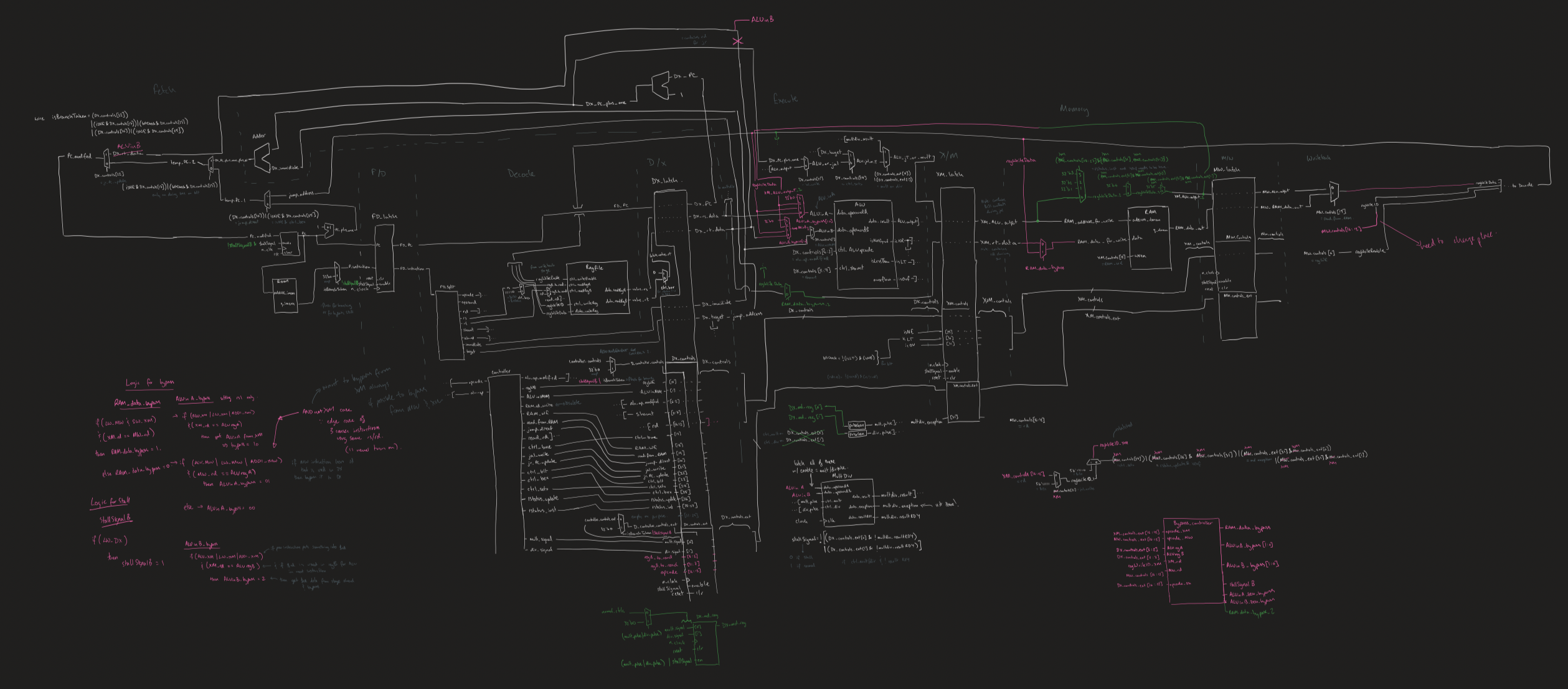

I have included a diagram (end of this section) I made while creating the CPU to show the scale of the datapath, not including the intricacies of each component (such as the wallace tree multiplier not being drawn out for obvious reasons). Some features are highlighted below:

- » 32-bit 100MHz processor

- » Pipelined and Bypassed

- » Handles hazards (no invalid computations returned)

- » Wallace Tree multiplier

- » Restoring Division Divider

- » CLA adder/subtractor

Everything from the logic gates to the DFFs to the entire datapath was created by myself. Source code can be found on the GitHub repository.