🝆 Foresee

github.com/ysarch-lab/foresee

This project started from my summer at Yale researching under Professor Abhishek Bhattacharjee and

soon to be Professor Raghavendra Pradyumna Pothukuchi.

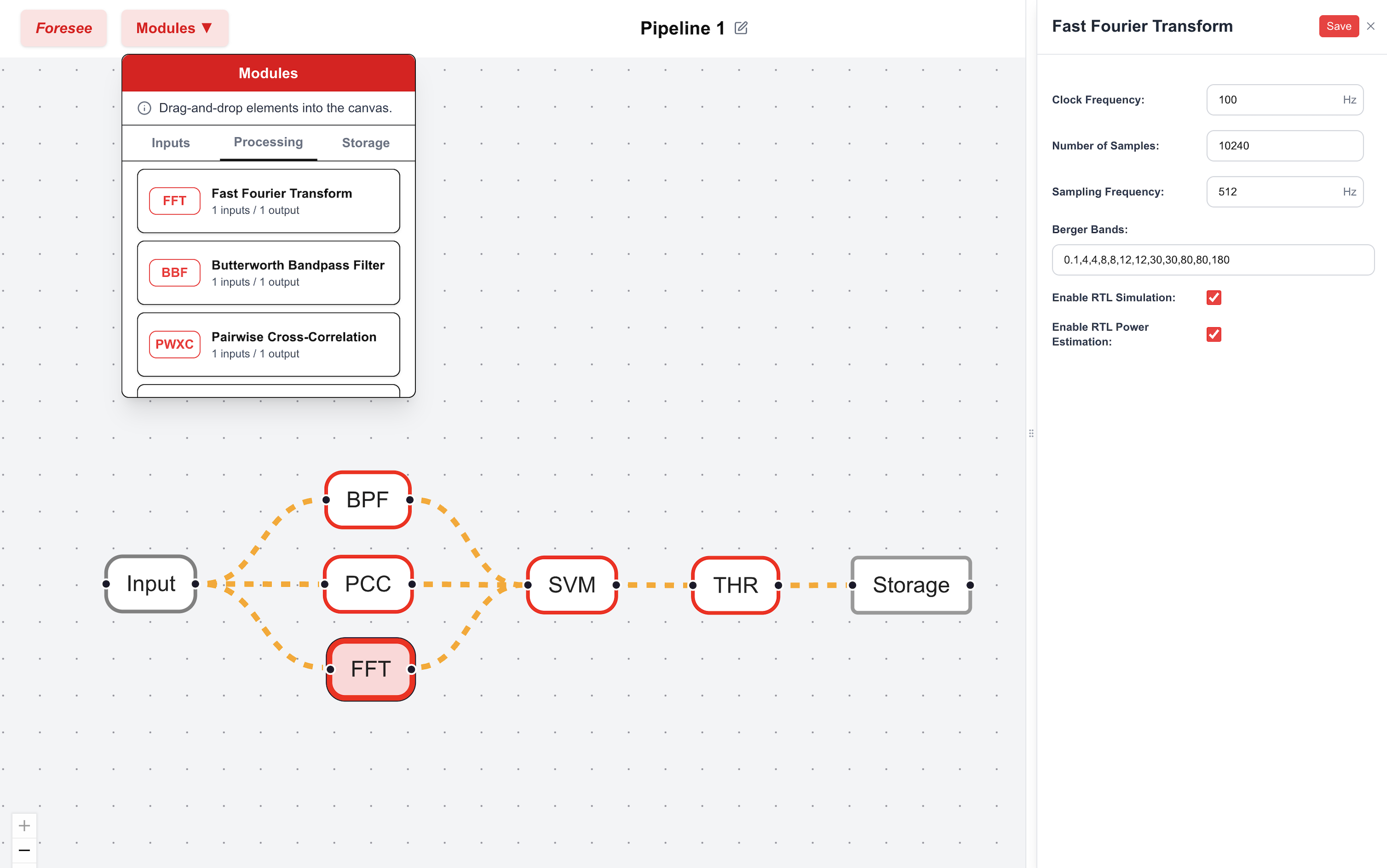

I started out making specific hardware blocks building on the lab's previous works HALO and SCALO, such as a verilog FFT block,

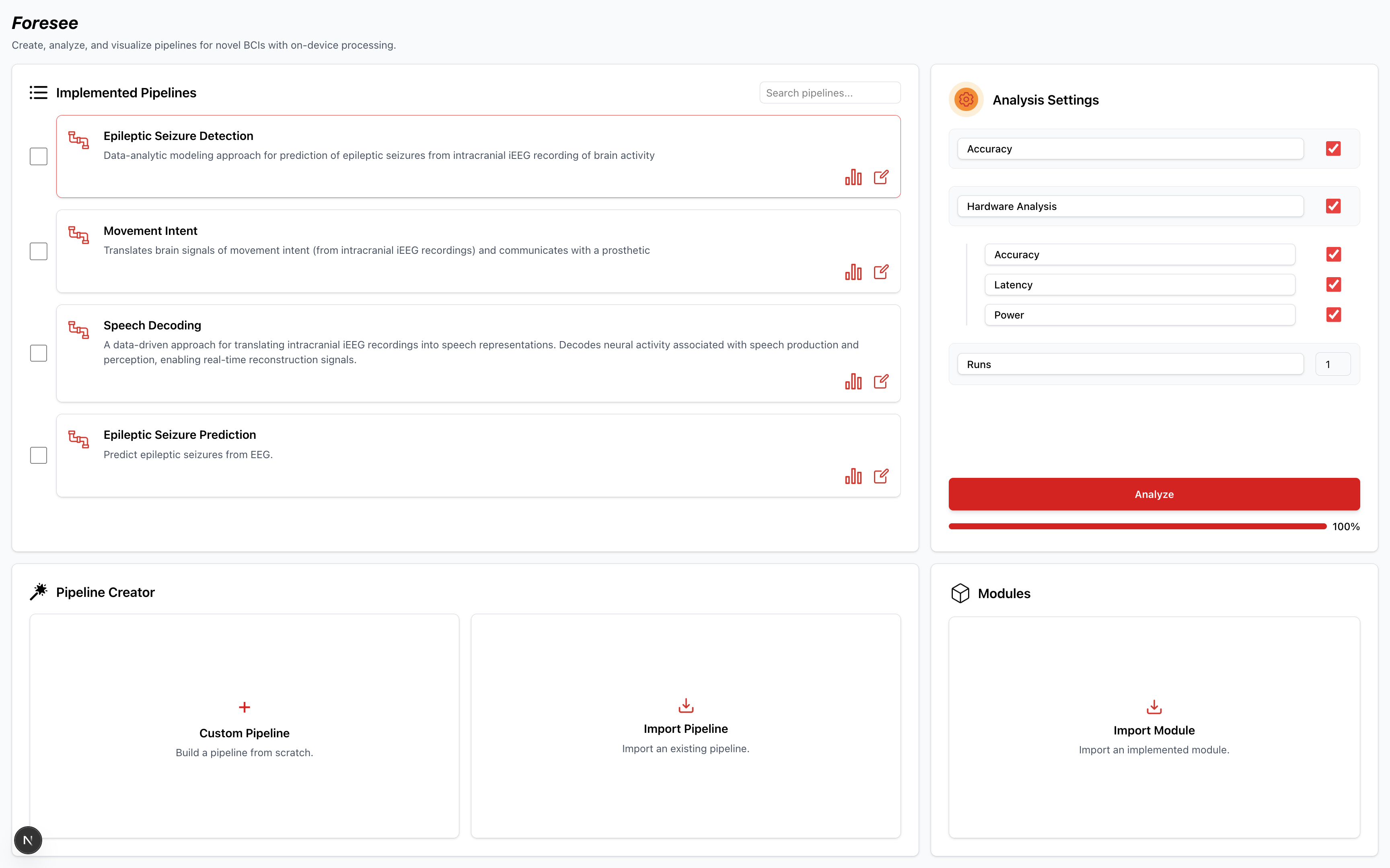

but soon realized that the lab - and the BCI community as a whole - needed a more general purpose framework for co-designing BCI processors with their algorithms.

The resulting paper was accepted at IEEE EMBS 2025, which is the world's largest biomedical engineering conference.

Once available, link to paper will be added here.

Abstract— Brain-computer interfaces (BCIs) with processing integrated on the device enable fast and autonomous closed-loop interaction with the brain. While such BCIs are rapidly gaining traction, they are also difficult to design due to the tight and conflicting power and performance needs of on-device processing. Meeting these specifications often requires the BCI processors to be co-designed with applications and algorithms, with processor designers and computational neuroscientists working closely to converge on the target hardware platform. But, this process has traditionally been cumbersome and ad hoc, due to the lack of systematic design space exploration frameworks. In response, we present Foresee, a new framework for fast exploration of BCI processors. Foresee offers a unified and modular interface for iteratively co-optimizing BCI processors with their algorithms, without sacrificing accuracy, speed, or ease of use. Foresee is publicly available, and comes with a library of hardware blocks for common signal processing functions that the community could contribute and build on. We demonstrate Foresee's utility and capability by analyzing on-device processing for two seizure detection methods from prior work, and validating our analysis on real hardware. We expect Foresee to be vital in designing next-generation BCIs